# HiAE: A High-Throughput Authenticated Encryption Algorithm for Cross-Platform Efficiency

Han Chen<sup>1</sup>, Tao Huang<sup>1</sup>, Phuong Pham<sup>1</sup> and Shuang Wu<sup>1</sup>

Huawei International Pte. Ltd., Singapore, concyclics@gmail.com, {huangtao80, pham.phuong, Wu.Shuang}@huawei.com

**Abstract.** This paper addresses the critical challenges in designing cryptographic algorithms that achieve both high performance and cross-platform efficiency on ARM and x86 architectures, catering to the demanding requirements of next-generation communication systems, such as 6G and GPU/NPU interconnections. We propose HiAE, a high-throughput authenticated encryption algorithm optimized for performance exceeding 100 Gbps and designed to meet the stringent security requirements of future communication networks. HiAE leverages the stream cipher structure, integrating the AES round function for non-linear diffusion.

Our design achieves exceptional efficiency, with benchmark results from software implementations across various platforms showing over 340 Gbps on x86 processors and 180 Gbps on ARM devices in AEAD mode, making it the fastest AEAD solution on ARM chips and setting a new performance record on the latest x86 processors.

**Keywords:** High-throughput · Authenticated Encryption · 5G/6G · AES-NI

# 1 Introduction

The growing demand for high-performance and secure cryptographic algorithms is driven by rapid advancements across various fields of modern communication and data transmission technologies. As data transmission rates continue to rise, particularly with the anticipated arrival of 6G, where speeds are expected to exceed 100 Gbps [LAL<sup>+</sup>19], the pressure on cryptographic systems to balance both security and performance becomes increasingly critical. This trend extends well beyond mobile communication networks, influencing diverse sectors such as high-performance data centers, AI and machine learning, Ethernet communication, software-defined networks (SDN), and Cloud Radio Access Networks (Cloud RAN).

In high-performance computing (HPC) environments, such as data centers, the demand for high-bandwidth communication between servers and storage devices is pushing the limits of interconnects, with speeds reaching 100 Gbps to 400 Gbps or more for data center backbone links. Similarly, in AI and machine learning, accelerators like Nvidia's NVLink, capable of transferring data at rates up to 1,800 GB/s, are driving the need for encryption solutions that can keep pace with the high-speed interconnects used in distributed training of large-language models [Corc]. Furthermore, with the growing deployment of 100GbE and 400GbE Ethernet networks in data centers and enterprise environments, cryptographic algorithms must perform efficiently at ultra-high throughput levels to ensure secure data exchange without compromising performance.

In SDN and Cloud RAN, the demand for high-speed encryption is particularly pronounced. These architectures rely on efficient data processing across distributed environments, where cryptographic algorithms are tasked with securing high-volume data flows.

The encryption solutions must operate efficiently on general-purpose CPUs, including both x86 and ARM platforms, which are the backbone of most computing infrastructures in these domains.

Modern hardware advancements, particularly Single Instruction Multiple Data (SIMD) instructions, have enabled significant performance gains in cryptographic algorithms. SIMD allows parallel execution of operations like XOR and modular arithmetic, leveraging instruction sets such as Intel's SSE/AVX/AVX2/AVX512 [Cor24b] and ARM's NEON [Com24a]. Moreover, the widespread support for AES-NI [Cora] and NEON cryptographic extension [BS12], optimized for AES round functions, has made it a cornerstone for high-performance cryptographic primitives. However, while AES-based designs like AEGIS [WP14] and Rocca [SLN+22] have demonstrated potential for 5G and early 6G requirements, they still face challenges in achieving cross-platform efficiency, especially as ARM architecture has been widely used for edge and mobile devices which require more on wireless communication ability.

#### 1.1 Motivation

Many recent cryptographic designs have utilized SIMD instructions to achieve high performance, particularly on x86 platforms using AES-NI. AES-NI has become the foundation for many recent high-speed (authenticated) encryption algorithms like AEGIS, SNOW-V [EJMY18], and Rocca, which are tailored to take advantage of the parallelism and efficiency offered by these instructions. However, these designs often neglect the architectural differences between x86 and ARM, where SIMD instructions are implemented via NEON rather than AES-NI. This oversight results in inconsistent performance when deploying these algorithms on ARM-based devices, which dominate mobile and embedded systems.

The transition to 6G, with its demand for ultra-high data rates and reliance on SDN or cloud RAN, further emphasizes the need for cryptographic algorithms optimized for diverse platforms. While some existing designs achieve remarkable performance on x86—reaching or exceeding 100 Gbps—these same algorithms often perform suboptimally on ARM platforms due to differences in SIMD instruction sets and hardware support for AES round functions. This gap highlights the pressing need for a unified approach that ensures high and consistent performance across both architectures.

Addressing this challenge requires rethinking cryptographic design to leverage the unique capabilities of each platform while maintaining compatibility and efficiency. This motivates our work in developing a cross-platform cryptographic primitive that achieves competitive performance on both x86 and ARM architectures, meeting the stringent demands of 6G systems.

#### 1.2 Contributions

This work addresses the challenges of designing cryptographic algorithms that achieve high performance and cross-platform efficiency for both ARM and x86 architectures, ensuring suitability for next-generation communication systems. The main contributions of this paper are as follows:

Cross-Platform Pipeline Optimization Analysis. We conduct a thorough analysis of the pipeline architectures of modern ARM and x86 processors, examining the nuances of their SIMD instruction sets and cryptographic capabilities. Our investigation focuses on key factors such as instruction throughput, latency, and execution unit utilization to identify architectural differences that influence performance. Based on this analysis, we derive the optimal ratio between AES round instructions and SIMD XOR instructions, ensuring efficient pipeline utilization tailored to the distinct characteristics of each platform.

A New Cross-Platform efficient AEAD Design. We design a new high-performance authenticated encryption with associated data (AEAD) algorithm, utilizing an innovative cross-platform structure as build block. We would like to highlight the following contributions in our design:

- Cross-Platform High-Throughput Structure: We introduce a novel XAXX structure that optimizes performance across both x86 and ARM platforms. This structure balances AES and XOR operations to achieve high instruction-level parallelism and efficient pipeline usage, adapting to the architectural differences between the platforms.

- Efficient Update Function: The update function efficiently integrates message blocks and optimizes AES operations while ensuring robust security. Compared to previous designs like Rocca, our design improves upon it by reducing the number of AES instructions needed to process a 128-bit plaintext from 3 to 2, minimizing data dependencies and carefully managing internal state updates. While the same level of security is maintained, our design boosts performance, bringing it closer to the maximum capabilities of available resources.

We also perform a comprehensive security analysis of our design, demonstrating its robustness against a wide range of attacks, including differential, linear, forgery, state recovery, and integral attacks.

Comprehensive Benchmarking Across Devices. We conducted extensive benchmarking of the proposed cipher across a wide range of devices, including both mobile processors and server-grade CPUs, to comprehensively evaluate its performance. Our experimental setup covered the latest x86 platforms as well as ARM-based architectures to ensure a robust and diverse evaluation.

The results of our benchmarks demonstrate that the proposed cipher achieves exceptional performance. Specifically, on the latest x86 CPUs, the cipher achieves a throughput of 340 Gbps, marking the best performance reported to date. Similarly, on ARM CPUs, it achieves an impressive 180 Gbps, outperforming all previous designs on ARM architectures.

These results highlight the efficiency of our design and its ability to leverage the advanced instruction sets available in modern x86 and ARM processors. By achieving such high performance, our cipher not only ensures robust security but also meets the demanding throughput requirements of contemporary applications, making it a state-of-the-art solution in its category.

### 1.3 Organization of the Paper

The organization of the rest of this paper is as follows:

Section 2 discusses the AES and SIMD instructions, providing a cross-platform analysis. In Section 3, we present the detailed specification of HiAE. The design rationale behind our approach is elaborated in Section 4. Section 5 covers the security analysis, ensuring the robustness of our design. In Section 6, we evaluate the performance of the proposed methods. Finally, the paper concludes in Section 7.

# 2 AES Instructions and SIMD Optimization: Cross-Platform Analysis

AES is widely used for securing data confidentiality. To enhance the efficiency of AES computations, most modern processors integrate AES-specific cryptographic instructions into their SIMD instruction sets. This integration is especially notable in the two most widely adopted processor architectures: Intel's AES-NI (Advanced Encryption Standard

New Instructions) [Cora] on x86 and the NEON cryptographic extension [Com24a] on ARM. By leveraging these AES instructions, processors can execute AES round functions significantly faster than traditional software implementations.

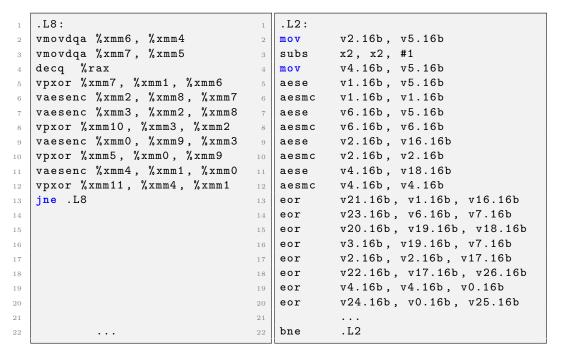

# 2.1 The Implementation difference of AES Instructions between x86 and ARM architectures

The implementation of AES instructions varies between x86-64 and ARM processors. In x86-64 processors, the AES-NI set set provides several instructions for the AES round function, including both the internal rounds and the final round. These instructions include:

```

\operatorname{aesenc}(S,K) = (\operatorname{MixColumns} \circ \operatorname{ShiftRows} \circ \operatorname{SubBytes}(S)) \oplus K\operatorname{aesenclast}(S,K) = (\operatorname{ShiftRows} \circ \operatorname{SubBytes}(S)) \oplus K

```

Conversely, the ARM NEON cryptographic extension separates the *MixColumns* operation, providing distinct instructions to handle this transformation to maintain the difference of internal and final round:

```

aese(S, K) = (ShiftRows \circ SubBytes(S \oplus K))

aesmc(S) = MixColumns(S)

```

The differences between ARM NEON and Intel AES-NI mostly are:

- AES-NI performs the XOR operation at the end of each round, while NEON executes the XOR operation at the beginning.

- AES-NI includes final round instructions that omit the *MixColumns* step, while NEON provides separate instructions for the *MixColumns* operation.

Consequently, to simulate an x86's AESENC instruction in ARM CPU, one more XOR instruction would be needed.

#### 2.2 Analysis of the Pipeline, Parallelization and SIMD Throughput

When a CPU core processes instructions, it first fetches and decodes the instructions in the front-end, then routes them to different execution units in the back-end for computation. Performance is constrained by both the front-end decoding and the execution units in the back-end. Most modern processors feature a 4-wide or wider decode capability, which surpasses their throughput for AESR and XOR operations, where we use AESR to generalize the AES instructions in x86 and ARM platforms in a uniform way. Therefore, our focus in this work is on the back-end performance.

According to [Corb] and recent work [BBL<sup>+</sup>24], on latest x86 platforms, there are typically 3-4 execution units for different SIMD instructions, with usually 1-2 units dedicated to processing AESR instructions. In contrast, lightweight ARM processors, especially those designed for mobile devices, typically have only 2 SIMD units, with 1-2 of these supporting cryptographic instructions. This results in a weaker pipeline parallelism capability for XOR and AESR operations on ARM processors compared to their x86 counterparts. And for the high performance ARM processors for laptop and desktops, like Apple Silicon's Performance Core, there will be 4 SIMD units with fully support of AES.

To evaluate the performance of an instruction I, there are two main metrics:

• Latency: the number of clock cycles between the beginning to the return of its result, we marked as Lat below.

• **Throughput**: the number of instructions that can be processed in a given amount of time, we marked as **TP** below.

**Pipeline Specifications**. We summarize most popular ARM and x86 architectures and their AESR, XOR instructions latency and throughput as well as the pipeline unit occupied in Table 1. For x86 devices, we only remain the relevant units from  $P_0 - P_6$ , while for ARM devices, we category them to 2-SIMD, 3-SIMD, 4-SIMD and 6-SIMD platforms and number the SIMD unit as  $V_*$ . For Apple Silicon's Efficiency Cores, according to Apple Silicon CPU Optimization Guide [Inc24], ASIMD/FP units in E-Core can do 1 AES instructions per 2 cycles, so the throughput will be half of the number of execute units.

Conditions for Fully Utilizing the Pipeline. To fully utilize the pipeline, the ratio of AESR and XOR instructions must align with the pipeline's execution capacity. Let a represent the number of execution units capable of processing AESR instructions, b the total number of execution units, and x:y the ratio of AESR to XOR instructions. Let C be a constant positive integer.

In order to fully utilize the pipeline, the following conditions must be satisfied:

- $x + y = C \cdot b$ : This condition ensures that the total workload of SIMD instructions matches the pipeline's available execution capacity.

- $y: x \ge (b-a): a$ : This condition ensures that AESR instructions can run in parallel with XOR instructions. While most units handle XOR, only some support AESR. By substituting AESR with XOR, we maintain parallelism. However, too many AESR instructions can create contention, leaving XOR-only units underutilized.

We define the a:b ratio as the AESR-SIMD ratio, which helps us better understand how different processors manage the balance of AESR and XOR instructions to fully utilize the SIMD pipeline.

#### 2.3 Instruction Fusion on ARM Devices

Since some NEON instructions like aese and aesmc are often processed together, recent ARM architectures can accelerate certain instruction pairs in an operation called fusion. For example, instructions like aesmc(aese(a, b)) and eor(eor(a, b), c) can benefit from this fusion to achieve higher IPC. These features should follow the optimization guide of each specific architecture, from Cortex-A77 (see Section 4.13 "Instruction Fusion" in [Com19b]) to later architectures.

# 3 The Specification of HiAE

Building on the analysis of AES instructions and SIMD optimization across x86 and ARM platforms, we now turn to the specifications of the proposed authenticated encryption design. This section outlines the structural and operational details of the cipher, highlighting how the cross-platform optimizations discussed earlier are integrated into its design. In Section 4, we will delve deeper into the rationale behind these design choices, focusing on how they balance performance, security, and efficiency across diverse hardware architectures.

#### 3.1 Notations

- $AESL(x) = MixColumns \circ SubBytes \circ ShiftRows(x)$ **Note:** This differs from AESR, which is the generalized notation for the AES instruction applicable to both x86 and ARM platforms.

- $x \oplus y = XOR(x, y)$

**Table 1:** Comparison Pipeline of Different Architectures [AR19, Com22b, Com16, Com22a, Com23a, Com18, Com19a, Com19b, Com20, Com22c, Com23b, Com24b, Com21b, Com22d, Com23c, Com22e, Com24d, Com22f, Com22g, Com24e, Com24c, Inc24]

| Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Instructions      | Lat  | TP  |       | ex    | ecutio | on un | its   |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|-----|-------|-------|--------|-------|-------|-------|

| x86 architecture p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | rocessors         |      |     | $P_0$ | $P_1$ | $P_2$  | $P_3$ | $P_5$ |       |

| I+-1 II11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | AESENC            | 7    | 1   |       |       |        |       | *     |       |

| Intel Haswell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XOR               | 1    | 3   | *     | *     |        |       | *     |       |

| I-+-1 Cl1-1-/C1- I -1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | AESENC            | 4    | 1   | *     |       |        |       |       |       |

| Intel Skylake/Cascade Lake                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | XOR               | 1    | 3   | *     | *     |        |       | *     |       |

| Intel Ice Lake                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AESENC            | 3    | 2   | *     | *     |        |       |       |       |

| interice dake                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XOR               | 1    | 3   | *     | *     |        |       | *     |       |

| Intel Alder Lake/Sapphire Rapids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AESENC            | 3    | 2   | *     | *     |        |       |       |       |

| inter Aider Lake/Sappinre Rapids                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | XOR               | 1    | 3   | *     | *     |        |       | *     |       |

| AMD Zen 1/2/3/4/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AESENC            | 4    | 2   | *     | *     |        |       |       |       |

| , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | XOR               | 1    | 4   | *     | *     | *      | *     |       |       |

| ARM architecture processors w                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   | nits |     | $V_0$ | $V_1$ |        |       |       |       |

| ADM Contor AEE/AE7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | AESE/AESMC        | 3    | 1   | *     |       |        |       |       |       |

| ARM Cortex-A55/A57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XOR               | 3    | 2   | *     | *     |        |       |       |       |

| ADM C+ A510/A590                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AESE/AESMC        | 3    | 2   | *     | *     |        |       |       |       |

| ARM Cortex-A510/A520                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | XOR               | 3    | 2   | *     | *     |        |       |       |       |

| ADM C + AZZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AESE/AESMC        | 2    | 1   | *     |       |        |       |       |       |

| ARM Cortex-A75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XOR               | 3    | 2   | *     | *     |        |       |       |       |

| ADM C + AZC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AESE/AESMC        | 2    | 1   | *     |       |        |       |       |       |

| ARM Cortex-A76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XOR               | 2    | 2   | *     | *     |        |       |       |       |

| ADM C ARRIAGO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AESE/AESMC        | 2    | 2   | *     | *     |        |       |       |       |

| ARM Cortex-A77/A78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XOR               | 2    | 2   | *     | *     |        |       |       |       |

| ADM C A TIP / A TOO / A TOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AESE/AESMC        | 2    | 2   | *     | *     |        |       |       |       |

| ARM Cortex-A715/A720/A725                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | XOR               | 2    | 2   | *     | *     |        |       |       |       |

| A DA CALLANDA A | AESE/AESMC        | 2    | 2   | *     | *     |        |       |       |       |

| ARM Neoverse-N2/N3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | XOR               | 2    | 2   | *     | *     |        |       |       |       |

| HICH THE LANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AESE/AESMC        | 3    | 1   | *     |       |        |       |       |       |

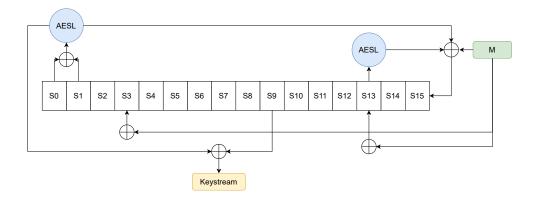

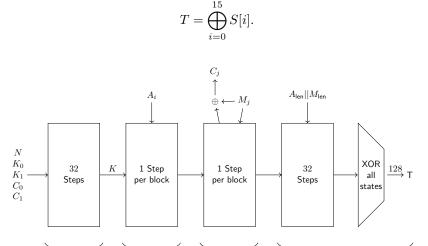

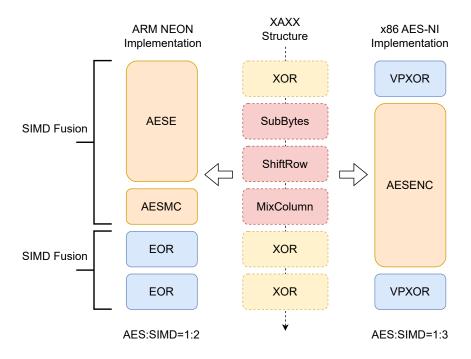

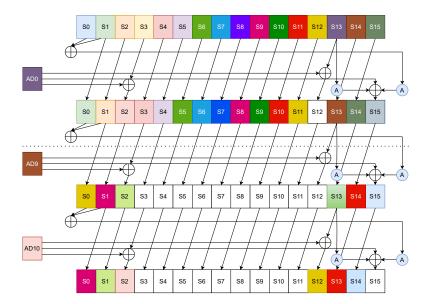

| HiSilicon Taishan V110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XOR               | 2    | 2   | *     | *     |        |       |       |       |